ESD释义:

ESD全称是Electro-Static discharge,其中文意思是“静电放电”。是指具有不同静电荷电位的物体相互靠近或直接接触引起的电荷转移。简单说就是电荷瞬间从一个物体移到另一个物体上,形成一个电荷转移的过程的现象,即具有不同静电电势(电位差)的物体或表面之间的静电电荷转移,就是静电放电。在EMC领域我们习惯上称之为静电放电抗扰度试验,具体可参阅国际标准IEC-61000-4-2/GBT 17626.2。其中分接触放电和电磁场击穿介质放电。

ESD实例:

(1)在雷雨天气产生的闪电,因为空气中有些尘埃粒子等所累积的正电与大地的负电相遇所产生放电的现象。

(2)在干燥天气时,你触摸另一个人产生的电击感觉。

(3)在铺有地毯的地板上行走后,手接触金属门把手产生的电击。

(4)在冬天梳头发时,或者脱毛衣时产生的电火花现象。

ESD产生原理:

具有不同静电荷电位的物体由于直接接触或静电感应所引起的物体之间静电电荷的转移。通常指在静电场的能量达到一定程度之后,击穿其间介质而进行放电的现象。

电荷的概念:

电荷是物质、原子或电子等所带的电的量。单位是库仑(记号为C)。我们常将“带电粒子”称为电荷,但电荷本身并非“粒子”,只是我们常将它想像成粒子以方便描述。电荷只是量度而已,(世界上每样东西都带电荷,只是它本身由于带两种一正一负,且数量均等的电荷,才相互抵消。)

分子:保持物质化学性质的一种微粒;

原子:化学变化中的最小微粒,原子中心的原子核有质子和中子,环绕原子核运转的是电子;

电子:具有最小电量的质量最小的粒子(现在有分数电量之说);

离子:以带正电(正离子)或负电(负离子)的原子或分子形态存在。

单晶体:按照一定规则的原子序列构成的晶体;

多晶体:小的单晶体的集合;

晶体:由反映晶体特征的基本单元在三维空间堆积而成的。把基本单元叫做晶胞;

质子数目=电子数目 =〉电中性

质子数目>电子数目 =〉正电性

质子数目<电子数目 =〉负电性

同性电荷相斥,异性电荷相吸,并且导体上的电荷是可移动的,而绝缘体上的电荷是不可移动的,这就意味着绝缘体上的电荷是不能通过接地来中和的。

静电的产生:

静电产生的两种途径,静电是一种静止的电荷,是电子不均匀分布的结果,主要是摩擦产生,其他像电场诱发,直接充电等,即摩擦起电与感应起电。

影响电荷量的因素:

摩擦电荷的极性与强度是由摩擦电序列决定,湿度愈高,静电愈低。55%湿度的静电产生量约为10%湿度的5-20%。其中还与电荷产生的速度;摩擦起电的相对位置;接触紧密程度;摩擦系数;分离速度.放电速度:材料的电导率;相对湿度;表面水汽分布;再接触的速度等甚至是还伴随一些不确定因素有关系。

1. 摩擦起电

a)当两种不同性质的材料(至少其中一个为绝缘体)接触和分离,电荷从一种材料转移到另一种材料。

b)得到电荷的材料呈负电性,反之亦然。

c )产生电荷的类型与两种材料的相对位置有关。

任何两种材料摩擦后电极性都是可以判断的,在摩擦起电过程中,两者的距离越远,则各自产生的电荷越多。

2. 感应起电

a) 非接触的方法

b) 当导电材料充分接近时,来源于某静电源的静电场将引起该导电材料表面的电荷分离。

ESD静电放电模型:

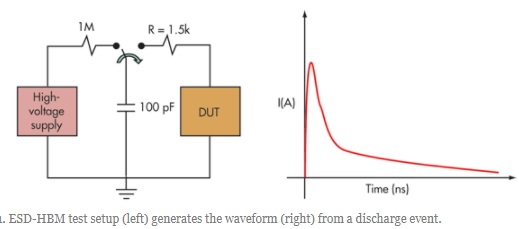

(1)HBM 人体放电模型(Human-Body Model, HBM)

人体模型(Human Body Model - HBM),HMB是ESD模型中建立最早和最主要的模型之一。

HBM是传统的测试模式,定义在工业标准 (MIL-STD-883x)中。人体上带电,特别在干燥的冬天,常会接触如门把手时便会有被电到的感觉。这是人体活动的结果,静电荷积聚在人体上,当我们去接触芯片时,人体上的静电就经由IC的pin脚进入芯片内部,然后经由IC放电到地。(不只在接触PIN时才会发生,因为封装IC的表面就存在静电荷,接触包装表面也会发生。)放电过程在瞬间发生,大概几纳秒内将IC组件烧毁。

(2)MM 机器放电模型 (Machine Model, MM)

机器放电模式,也就是将人体换成了机器设备,主体部分的改变,使得测试模式的改变。在这情况下,指静电电荷积累在机器设备上,当接触到IC进对芯片放电,并因此毁坏了电路。机器放电模式,工业标准EIAJ-IC-121 method20。MM测试电路与HBM相似,数值改变如,电容值为200pf,充电电压500V,充电电阻100Mohms,放电部分加>500nH电感(电感量与电流无关,感抗XL=2πfL,f为频率)。因为绝大部分机器是金属的,等效电阻极小,导致瞬时放电电流巨大(几安培)。机器模型因在日本得到广泛应用,也叫日本模型。与家具模型不同的是它主要由200pf电容串非常低的电阻(<10Ω)代替通常串联的电阻构成。机器模型的典型代表如带电绝缘的机器人手臂、车辆、绝缘导体等。机器模型放电的波形与预料的家具模型波形相似,不同的是带电电容较大。典型的机器模型对小电阻(<10Ω)放电的波形, 峰值电流可达几百安培,持续时间(决定于放电通路的电感)为几百纳。

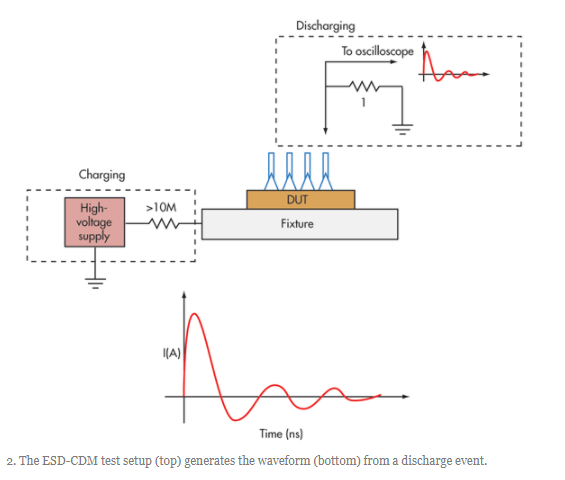

(3)CDM 组件充电模式 (Charged-Device Model, CDM)

这种模式下,电荷积聚在IC本身,可能是因为与PIN摩擦,或者是接触到其他物体的静电电荷,使本身带电。再通过直接接地或间接接地进行放电,而形成的一种放电现象。此类现象的模拟十分困难,是因为导致放电的组件差异所造成的。这种现象表明IC可能在生产过程中受损,比如IC在传输过程中带电,在安装到电路板上时接地而损坏。有时也可能在测试过程中受到损坏。CDM等效电路因情况的不同而多种多样。因为封装很小,所以电容和电感值都很小,大约5pf和10nH。CDM的放电时间很短,电流能在1ns时间内冲到15安培的高峰,因此这种现象更容易对IC造成损伤。CDM与HBM没有相互关连性,成功的CDM测试不能预示器件用HBM会发生什么情况!

(4)其它FIM/IEC/E-Gun 电磁场感应模式 (Field-Induced Model, FIM)

此类模式与CDM相似,只是IC带电方式不同。这种模式是IC在电场环境中,因感应而使本身带电,放电模式与CDM类拟。这种模式工业标准(JESD22-C101),详情请阅读相关标准。

来源:https://www.qiyingschool.com/news/47002.html

ESD Electrostatic discharge, 也就是所谓的“静电保护”。

Wikipedia里面是这样定义的:Electrostatic discharge (ESD) is the sudden flow of electricity between two electrically charged objects caused by contact。翻译过来呢,就是指两个储存有电荷的物体相互接触时候产生的瞬时电流。

最近作者君做的项目呢,对于ESD的要求比较严格,就经常和一个ESD部门的哥们讨论学习一下。他告诉我说,ESD可以在任何地方发生,无论是制造,生产,装配,测试,甚至运输及现场应用。当时我就有一种想放弃治疗的想法。。。。

那么,问题来了,我们怎么在电路中对其进行模拟并仿真呢?一般我们熟悉并且在电路仿真里面需要用到的模型有两种:CDM和HBM.

CDM就是所谓的Charge Device Model,HBM就是所谓的Human Body Model。

两者对比可以看出,一般来说CDM的电流比HBM的电流大一些、也快一些,因为并无较大的电阻在放电通路上面限制放电的过程。

因此,在ESD的仿真中,需要在supply上添加这样一个pulse电压。例如:CDM情况下,supply上面需要加入一个高达15V的pulse,上升沿和下降沿都是200ps,持续4ns。而在HBM的情况下,这个pulse的peak电压仅仅只是6V,上升沿和下降沿是2ns,持续时间400ns。

这里插入一句那个哥们的话:“我们就是计算这种 secondary 的ESD的相关数值给你们用的啦。”说罢,事了拂衣去,深藏身与名。。。

等等,为什么上来就说到了secondary ESD protection呢?既然有secondary ESD

protection,那primary ESD protection在哪里呢?

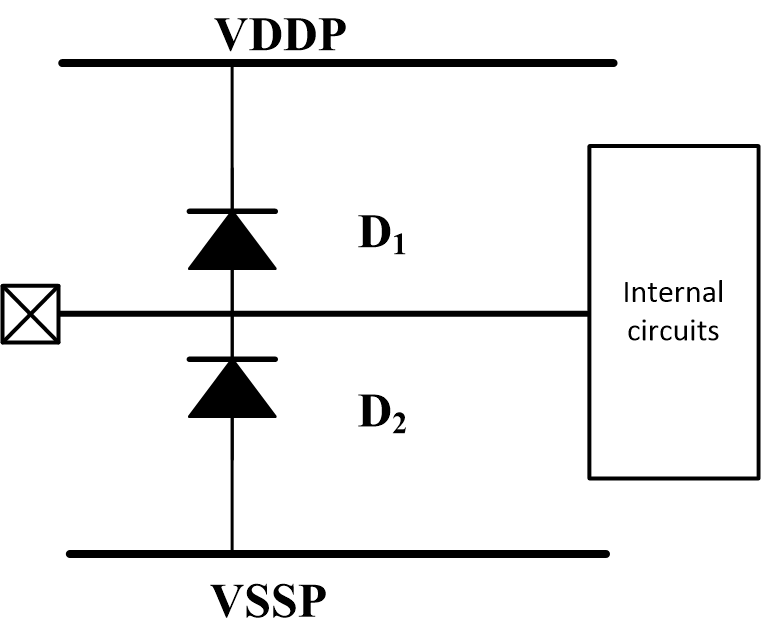

我们熟悉的IO结构,那种上下各有一个diode的pad,就是primary esd protection:

比如HBM模型里面,IO被加上一个+2000V的高压,则上面的diode D1就自然导通了,外界的高压顺着VDDP被迅速导走。同理,若是加上一个-2000V的高压,D2就导通了,大电流从VSSP快速流向IO,也未伤及内部的电路。

在这里,作者君想问大家一个问题:VDDP和VSSP都是给IO的diode们提供偏置的supply。那么VDDP和VSSP的IO 又当是怎么样的呢?还能上下各放一个diode吗?

快速思考一秒后……

肯定不能是这样的嘛!感觉就是不能这样……

那没有了上下两个diode,要如何保护VDDP和VSSP的IO呢?

因此,此处应当有另外的ESD保护电路在VDDP的IO和VSSP的IO之间。比如VDDP被加上+2000V的高压时,通过这个ESD diode快速导走高压电流。而当VDDP是0,而VSSP被加上+2000V的高压时,这个……

等等,容在下先想想,这里有两个方向相反的diode吗?

……

一秒后。

如果VSSP被加上了+2000V,那么岂不是所有的IO都挺热闹了?

为什么这么说?

嘿嘿,所有的nwell都是被VDDP给biased成为0V,而substrate因为VSSP变成了2000V,那么,岂不是所有的nwell和sub之间的寄生diode都被打开了?

哇!想想看,听起来好欢乐的场景啊!

墨白听说,还有一个所谓的“1 Ohm”原则,据说是从IO到那些esd diode之间的导通电阻必须要小于1 Ohm,以免寄生电阻太大,影响了快速放电的效果,避免有些“漏网之鱼”流到内部电路里面去了。所以大家若是仔细看看IO的版图,会发现那里metal真是密密麻麻的,“无所不用其极”。

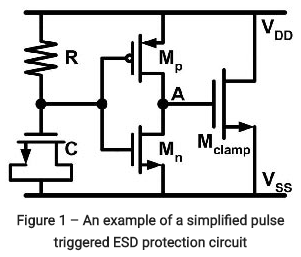

最后,再多说一个小的电路(懒得画图,所以拿别人的图借用一下):

这也是一个ESD的保护电路。为什么要说这个呢?因为作者君昨天刚刚被要求在自己内部的电路上面加一个nmos的switch,这个nmos的gate就是图中A点。而且被人告知,这也是secondary ESD protection。(请大家注意,这个fig.1是io的一部分,那个大的nmos并不是内部电路。我在说是内部电路可以使用io的内部节点进行控制)

我们简单分析一下:如果VDD上面有高压pulse的时候,因为电容的电压滞后作用,电容上面的电压并没有跟着VDD迅速提高。因此此时Mp的gate电压值比source小了不少,导致Mp导通,A点也被连到了VDD上面,巨大size的Mclamp被打开,VDD和VSS通过Mclamp连在了一起。这样一来,VDD上面的pulse就这样被巨大的Mclamp给导走了,因此,我们脆弱的内部电路也就被保护了起来